| Mata   |                                                                                                                                                                                                                                                                                                                                                                                                                                    | EE                                               |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| vvater | mark DEMO: Purchase from www.A-PDF.com to remove the watermark                                                                                                                                                                                                                                                                                                                                                                     |                                                  |

| USN    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                 | EC/TE7                                           |

|        | Seventh Semester B.E. Degree Examination, June/July 201                                                                                                                                                                                                                                                                                                                                                                            | 6                                                |

|        | <b>Computer Communication Networks</b>                                                                                                                                                                                                                                                                                                                                                                                             |                                                  |

| Time   | 2: 3 hrs. Max. M                                                                                                                                                                                                                                                                                                                                                                                                                   | Aarks:100                                        |

|        | Note: Answer any FIVE full questions, selecting<br>atleast TWO questions from each part.                                                                                                                                                                                                                                                                                                                                           | 195                                              |

|        | PART – A                                                                                                                                                                                                                                                                                                                                                                                                                           | .Dx                                              |

| ł      | <ul> <li>a. Explain the ISO – OSI reference model with suitable diagram. Discuss the funct layer.</li> <li>b. Describe the SS7 signaling and services with suitable model.</li> <li>c. The internet users in the year January – 2015 is 50,000. It will roughly doubling every 18 months. What is the expected number of internet users in the year Decenter.</li> </ul>                                                           | (10 Marks<br>(06 Marks<br>g in size fo           |

| ł      | <ul> <li>a. Generate CRC code and check if there is any error in the code word. If data wand divisor is 1011. How these are implemented using encoder and decoder?</li> <li>b. Explain stop-and-wait ARQ protocol with suitable timing diagram.</li> <li>c. A channel has a bit rate of 4 Kbps and a propagation delay of 20 msec. For what frame sizes does stop and wait protocol give an efficiency of at least 50%?</li> </ul> | (10 Mark<br>(06 Mark                             |

| ł      | <ul> <li>a. Discuss the behaviour of the three persistence methods of CSMA.</li> <li>b. Discuss three channelization protocols.</li> <li>c. A group of N stations share a 56 Kbps pure ALOHA channel. Each station out bit frame on an average of once every 100 sec. What is the maximum value of N<sup>4</sup></li> </ul>                                                                                                        | (06 Mark<br>(09 Mark<br>puts a 100<br>? (05 Mark |

|        | <ul> <li>a. Explain 802.3 Ethernet frame format and addressing technique.</li> <li>b. Briefly discuss the distributed co-ordination function and point co-ordination 802.11 MAC sub-layer.</li> </ul>                                                                                                                                                                                                                              | (10 Mark<br>function (<br>(10 Mark               |

|        | PART – B                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                  |

| 5 a    | a. Discuss the loop problem in bridged LAN. How loop problems are solved in bridged                                                                                                                                                                                                                                                                                                                                                | idged LAN<br>(10 Mark                            |

|        | <ul><li>Differentiate between a bus back bone network and star back bone network.</li><li>What characteristics are used to group station in a VLAN?</li></ul>                                                                                                                                                                                                                                                                      | (06 Mark<br>(04 Mark                             |

|        | <ul> <li>a. Explain class full addressing. What are default masks?</li> <li>b. Find the class full address : <ul> <li>i) 125.05.13.8</li> <li>ii) 225.06.13.8</li> <li>iii) 14.23.120.5</li> <li>iv) 220.06.120.5.</li> </ul> </li> </ul>                                                                                                                                                                                          | (06 Mark<br>(04 Mark                             |

| C      | <ul> <li>An ISP is granted a block of addresses starting with 190.100.0.0/16. The IS distribute these addresses to three groups of customers as follows :</li> <li>i) The first group has 64 customers : each needs 256 addresses</li> </ul>                                                                                                                                                                                       |                                                  |

i) The first group has 64 customers ; each needs 256 addresses

ii) The second group has 128 customers ; each needs 128 address

iii) The third group has 128 customers ; each needs 64 addresses

Design the sub blocks and find out how many addresses are still available after these allocations. (10 Marks)

1 of 2

(10 Marks)

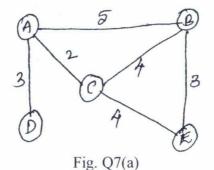

7 a. Explain the distance vector routing for following graph.

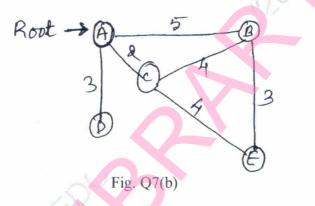

b. Find a shortest path three for following graph using Dijkstra algorithm.

(10 Marks)

(06 Marks)

(04 Marks)

- 8 a. Explain three way hand shake based connection establishment in TCP. (10 Marks)

- b. Explain the different field in UDP, with suitable diagram.

- c. Differentiate between connection less and connection-oriented service.

index fibers with appropriate mathematical equations. by a factor of 10. Assume V number as 2.405. 2 Discuss different types of non linear scattering losses. a. Silica has an estimated fictive temperature of 1400 K with an isothermal compressibility of b. constant is  $1.381 \times 10^{-23} \text{ JK}^{-1}$ . A step index multimode fiber with a core refractive index of 1.500, a relative refractive C. of curvature at which large bending losses occurs. 3 a.

- $7 \times 10^{-11}$  m<sup>2</sup>N<sup>-1</sup>. The refractive index and photoelastic co-efficient for silica are 1.46 and 0.286 respectively. Determine the theoretical attenuation in decibels per kilometer due to fundamental Rayleigh scattering in silica at optical wavelength of 0.63 µm. Boltzmann's (08 Marks)

- index difference of 3% and an operating wavelength of 0.82 µm. Estimate the critical radius (06 Marks)

Explain with the help of neat diagram, distributed-feedback (DFB) laser diode. (06 Marks)

- b. A double-hetrojunction In GaAsP LED emitting at a peak wavelength of 1310 nm has radiative recombination times of 30 and 100 ns, respectively. The drive current is 40 mA. Find the following:

- i) The bulk recombination life time.

- ii) The internal quantum efficiency.

- iii) Internal power level (assume electron charge as  $1.602 \times 10^{-19}$  C) (07 Marks)

- Discuss the operation of pin photodetector with appropriate diagrams. C. (07 Marks)

- 4 With appropriate mathematical equations explain single-mode fiber joints. (06 Marks) a.

- b. Explain fusion splicing of optical fibers with appropriate diagrams. Briefly describe the principal of operation of the following: C.

- i) Expanded beam connector.

- ii) Star couplers.

#### PART – B With a schematic diagram, explain the working of an optical receiver.

b. Explain the term receiver sensitivity. Derive an equation for receiver sensitivity in terms of photo detector noise. (08 Marks) Discuss coherent detection with relevant block diagram. C. (06 Marks)

Discuss the advantages of optical fiber communication. With the help of neat diagrams discuss the structure of single mode and multi mode step

**Optical Fiber Communication** Time: 3 hrs. Max. Marks:100 Note: Answer FIVE full questions, selecting

Seventh Semester B.E. Degree Examination, June/July 2016

at least TWO questions from each part.

# PART – A

1 of 2

**10EC/TE72**

1

a.

Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice

Important Note : 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

5

a.

- b.

- (06 Marks) c. Estimate the maximum core diameter for an optical fiber with refractive index difference of 1.6% and a core refractive index of 1.48, in order that it may be suitable for single mode operation for an operating wavelength of 0.9 µm. Further estimate the maximum core diameter for a single mode operation when the relative refractive index difference is reduced

- (06 Marks)

(08 Marks)

(06 Marks)

(06 Marks)

(08 Marks)

(06 Marks)

| a. | Discuss subcarrier multiplexing.                                              | (06 Marks)    |

|----|-------------------------------------------------------------------------------|---------------|

| b. | Explain link power budget with a relevant diagram.                            | (06 Marks)    |

| c. | Write a short note on:                                                        |               |

|    | i) Chirping.                                                                  |               |

|    | ii) Extinction ratio penalty.                                                 | (08 Marks)    |

| a. | Explain the principal of operation of WDM with relevant block diagram.        | (07 Marks)    |

| b. | Discuss the design and operation of a polarization independent isolator       |               |

|    | miniature optical components.                                                 | (06 Marks)    |

| c. | Explain with help of relevant diagrams various application of fiber Bragg gra |               |

|    |                                                                               |               |

| a. | With the help of energy level diagrams, explain the working of Erbiun         | m-Doped Fiber |

Amplifiers (EDFA). b. Write short notes on :

6

7

8

- i) SONET / SDH frame formats.

- ii) High-speed lightwave links.

(10 Marks)

(10 Marks)

**10EC/TE72**

USN

**10EC73**

## Seventh Semester B.E. Degree Examination, June/July 2016 **Power Electronics**

Time: 3 hrs.

1

Max. Marks:100

### Note: Answer any FIVE full questions, selecting atleast TWO questions from each part.

#### PART - A

- Explain the different types of power electronic converter circuits with neat circuit diagram a. and input and output waveforms. Also mention its application. (08 Marks)

- b Write the symbol and characteristic features of the following devices: (i) BJT (ii) TRIAC (iii) GTO (iv) MOSFET. (08 Marks)

- Discuss the peripheral effects of power electronic converters. Also write the remedies. C.

(04 Marks)

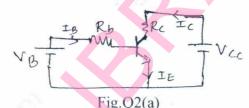

2 For the circuit shown in Fig.Q2(a), the BJT is specified to have  $\beta$  in the range of 12 to 75. If a.  $V_{cc} = 40 \text{ V}, \text{ } \text{R}_{c} = 1.5 \Omega, \text{ } \text{V}_{B} = 6 \text{ V}, \text{ } \text{V}_{CE(sat)} = 1.2 \text{ V} \text{ and } \text{ } \text{V}_{BE(sat)} = 1.6 \text{ V} \text{ and } \text{ } \text{R}_{b} = 0.7 \Omega.$ Calculate: (i) Overdrive factor ODF (ii) Forced B<sub>f</sub> (iii) Total power dissipation(P<sub>T</sub>)

(07 Marks)

- b. With the transient model of MOSFET explain switching characteristics.

- (06 Marks) c. What is the need for isolation for gate drive circuits? Discuss the different methods of providing isolation of gate drive circuits from power circuits. (07 Marks)

- 3 a. Explain the V-I characteristics of SCR by clearly indicating different states on characteristics. Also explain different modes of operation. (06 Marks)

- With two transistor analogy of a thyristor obtain the equation for anode current. b. (06 Marks)

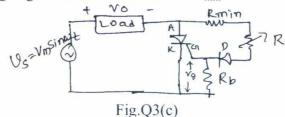

- An SCR employs an R-triggering as shown in Fig.Q3(c) with  $I_{g(min)} = 0.1$  mA and C.  $V_{g(min)} = 0.5$  V. The diode is silicon and the peak amplitude of the input voltage is 24 volts. Determine the triggering angle  $\alpha$  for R = 100 k $\Omega$  and R<sub>min</sub> = 10 k $\Omega$ . (04 Marks)

- d. A SCR has a di/dt = 50 A/ $\mu$ sec and dv/dt = 150 V/ $\mu$ sec. It operates on a 100 V, calculate the snubber circuit elements using approximate expressions. (04 Marks)

- With necessary circuit and waveforms explain the principle of operation of single phase a. semiconverter. Also derive an expression for the average output voltage. (06 Marks)

- With neat circuit diagram explain the operating principle of dual converter with and without b. circulating current. (08 Marks)

4

c. A single phase half wave controlled rectifier is used to supply power to 10 Ω load from 230V, 50 Hz supply at a firing angle of 30°. Calculate (i) average output voltage (ii) effective output voltage (iii) average load current. (06 Marks)

#### <u> PART – B</u>

- 5 a. What is the necessary condition for successful commutation of SCR? Compare between forced and natural commutation. (06 Marks)

- b. With necessary circuit and waveforms explain the working of complementary commutation. Also perform circuit analysis. (08 Marks)

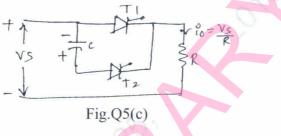

- c. For the impulse commutated thyristor of circuit Fig.Q5(c), determine the turn-off time of the circuit, if  $V_s = 200 \text{ V}$ ,  $R = 10 \Omega$ ,  $C = 5 \mu \text{F}$  and  $V_c(t = 0) = V_s$ . Also derive the equations used. (06 Marks)

- 6 a. With the help of neat circuit and relevant waveforms explain the working of ON-OFF control, for single phase AC voltage controller with resistive load. Also derive an expression for RMS output voltage.

(08 Marks)

- b. A 1 φ half wave ac voltage controller has an input voltage of 120 V, 60 Hz and a load resistance of 10 Ω. The firing angle of thyristor is 60°. Find

(i) RMS output voltage (ii) Input power factor (iii) Average input current. (08 Marks)

- c. What is the problem caused by sharp single pulse triggering in a 1 \$\overline\$ AC voltage controller when the load is inductive? How can this be solved? (04 Marks)

- 7 a. Briefly explain the classification of choppers with circuit, waveforms and quadrant diagrams. (08 Marks)

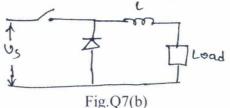

- b. For the chopper shown in below Fig.Q7(b), DC source voltage is 200 V, load resistance is 20 Ω. Consider the voltage drop of 4 V across chopper when it is ON. For a duty cycle of 0.6, calculate (i) Average and rms value of output voltage. (04 Marks)

- c. Explain the operation of step down chopper with RL load. Also derive an expression of peak-peak output ripple current. (08 Marks)

- 8 a. Explain the principle of single phase half bridge inverter with suitable circuit and waveforms. (10 Marks)

- b. Explain the performance parameters of inverter. (04 Marks)

- c. Explain principle of working of variable DC link inverter. Also mention advantages and disadvantages. (06 Marks)

USN

10EC74

# Seventh Semester B.E. Degree Examination, June/July 2016 Embedded System Design

Time: 3 hrs.

11/1 . .

Max. Marks:100

### Note: Answer FIVE full questions, selecting at least TWO questions from each part.

#### PART – A

| 1 | a. | embedded system? List out three kinds of computing engines that ar<br>embedded system.          |            |

|---|----|-------------------------------------------------------------------------------------------------|------------|

|   | b. | Briefly describe the major elements of embedded system development life cycle.                  | (04 Marks) |

|   | с. | Define: i) Watch dog timer ii) Instruction cycle                                                | (08 Marks) |

|   |    | iii) Hard real time system iv) Soft real time system                                            | (08 Marks) |

| 2 | a. | Briefly describe the more commonly used addressing modes.                                       | (08 Marks) |

|   | b. | Describe the four operations of instruction cycle in ISA and RTL level.                         | (06 Marks) |

|   | c. | Write short notes on finite state machines.                                                     | (06 Marks) |

| 3 | a. | Write short notes on:                                                                           |            |

| 5 | а. | i) Overlays                                                                                     |            |

|   |    | ii) Dynamic RAM with read and write operation timing.                                           | (08 Marks) |

|   | b. | A system specification requires an SRAM system that can store upto $4K \times 16$               |            |

|   | 0. | however the longest memory size available is $1K \times 8$ bit. Assume the proce                |            |

|   |    | 16 address and data lines. Show the SRAM design for the above specification w                   |            |

|   |    | write timing diagram.                                                                           |            |

|   | c. | Explain in detail direct mapped cache design with word size of 32 bits for:                     | (06 Marks) |

|   |    | i) Cache size of 64K words organized as 128 0.5k word blocks.                                   |            |

|   |    | <ul> <li>ii) Main memory size of 128 M words organized as 2k pages holding 128 block</li> </ul> | seach      |

|   |    | in) main memory size of 120 in words organized as 2k pages nording 128 block                    | (06 Marks) |

|   |    |                                                                                                 | (00 Marks) |

| 4 | a. | What is a product life cycle and explain briefly V life cycle and spiral mode.                  | (08 Marks) |

|   | b. | List out the five steps and its importance in the design process of a successfu                 |            |

|   |    | system design.                                                                                  | (06 Marks) |

|   | C. | Briefly describe the three areas that should be considered in static analysis of                |            |

|   |    | design.                                                                                         | (06 Marks) |

|   |    | PART – B                                                                                        |            |

| 5 | a. | Define thread. Enumerate the difference between a process and a thread.                         | (05 Marks) |

|   | b. | Write short notes on foreground/background system.                                              | (05 Marks) |

|   | C. | What is a scheduling strategy? Define the three general categories of scheduling                |            |

|   |    |                                                                                                 | (04 Marks) |

|   | d. | Explain the core responsibilities of operating system.                                          | (06 Marks) |

|   |    |                                                                                                 |            |

- a. Explain in detail about TCB (Task Control block) and its functions. (06 Marks)

b. Briefly explain about interrupts and its importance in developing kernel of embedded software. (06 Marks)

- (06 Marks)

(08 Marks)

c. Describe the different kinds of stack that one might find in an embedded application.

6

#### **10EC74**

- What is Amdahl's law? Consider a system with the following characteristics. The task to be 7 a. analysed and improved currently executes in 100 time units and the goal is to reduce execution time to 80 time units. The algorithm under consideration in the task uses 40 time units. Calculate the amount of improvement required. (05 Marks) (05 Marks)

- b. Write short notes on Big 'O' notation.

- c. Perform the complexity analysis for loop constructs:

- i) for loop

```

int sum = 0;

for (int j = 0; j < n; j++)

sum = sum + j;

ii) while loop

int prod = 1;

int n;

while (! Done)

{ prod = prod*n;

n – –;

if(n < = 1)

done = true;

}

```

(10 Marks)

- Define response time. Describe the major components of response time analysis of (i) polled 8 a. loop, (ii) pre-emptive schedule in an embedded application. (08 Marks)

- b. What are the common mistakes that might be made during performance optimization analysis? (05 Marks)

- c. How can we measure and reduce the effect that a software algorithm can have on power consumption? (07 Marks)

10EC751

# Seventh Semester B.E. Degree Examination, June/July 2016 DSP Algorithms and Architecture

Time: 3 hrs.

Max. Marks:100

# Note: Answer any FIVE full questions, selecting atleast TWO questions from each part.

## PART – A

- a. An analog signal is sampled at the rate of 8 KHz, if 512 samples of the signal are used to compute DFT, X(k), determine the analog and digital frequency spacing between adjacent X(k) elements. Also determent analog and digital frequencies corresponding to k = 64.

- b. List the major architectural features used in DSP system to achieve high speed program execution. (06 Marks)

- c. Explain the decimation and interpolation with equation. Let x(n) = [3, 2, -2, 0, 7]. It is interpolated using an interpolation filter  $b_k = [0.5, 1, 0.5]$  with interpolation factor-2. Determine the interpolation sequence. (08 Marks)

- 2 a. With a neat block diagram explain about the saturation logic and its use. (06 Marks)

- b. Briefly explain about the 4 × 4 Braun multiplier with its structure. In n × n parallel multiplier structure how many adders are required? (08 Marks)

- c. With a neat block diagram, explain address generation unit of DSP system. (06 Marks)

- 3 a. Compare architectural features of TMS320C25 and motarala fixed point DSP devices.

(06 Marks)

(06 Marks)

- b. Describe the multiplice/address unit of TMS320C54XX processor with a neat block diagram. (06 Marks)

- c. Consider that AR3 is selected as the pointer for the circular buffer. The various register contents are  $B_k = 40$ , AR3 = 1020H, AR0 = 0025H. Find : i) start and end address of the buffer ii) contents of AR3 after the execution of the instruction LD \*+AR3(12H)% iii) contents of AR3 after the instruction LD \* AR3 + 0%. (08 Marks)

- 4 a. Explain the operation of serial input/outputs ports and hard ware timer of TMS320C54XX on chip peripherals. (08 Marks)

- b. Differentiate between MAC and MACD instruction by way of explaining them. (04 Marks)

- c. By means of a figure, show the pipeline operation of the following sequence of TMS320C54XX instruction. Assume initial value of AR3 is 80h and the values. stored in memory locations 80h, 81h, 82h as 1, 2 and 3 LD \* AR3+, A ADD # 1000h, A STL A, \* AR3 +.

(08 Marks)

#### <u>PART – B</u>

- 5 a. What do you mean by Q-notations used in DSP algorithm implementation? What are the values represented by 16 bit numbers N = 4000h, in  $Q_{15}$ ,  $Q_7$  and  $Q_0$  notations? (08 Marks)

- b. Write an assembly language program for TMS32054XX processor to multiply two Q<sub>15</sub> numbers to produce Q<sub>15</sub> result. (05 Marks)

- c. With the help of a block diagram, explain the implementation of an FIR filter in TMS320C54XX processor. Show the memory organization for the filter implementation.

(07 Marks)

## **10EC751**

(08 Marks)

- Why zero padding is done before computing the DFT? 6 (02 Marks) a. Explain an 8-point DIT-DFT implementation structure based on the butterfly on the b. TMS320C54XX. (08 Marks) (10 Marks)

- Determine optimum scaling factor to prevent over flow. c.

- Draw the I/o interface timing diagram for read-write-read sequence of operation. (06 Marks) 7 a.

- Design an interface to connect a 64k×16 flash memory to a TMS320C54XX device. The b. processor address bus is  $A_0$  to  $A_{15}$ . (06 Marks)

- What are interrupts? How interrupts are handled by the C54XX DSP processor? (08 Marks) C.

- Explain with a neat diagram, the synchronous serial interface between the C54XX and a 8 a. CODEC device. (06 Marks)

- Explain the operation of pulse position modulation (PPM) to encode two biomedical signals. b.

- Describe with a suitable diagram a digital model for production of speech signal. (06 Marks) C.

| U                                                        | SN                |                | 10                                                                                                                                                                                                                          | EC/TE762                                              |  |  |  |  |

|----------------------------------------------------------|-------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| Seventh Semester B.E. Degree Examination, June/July 2016 |                   |                |                                                                                                                                                                                                                             |                                                       |  |  |  |  |

|                                                          | Real Time Systems |                |                                                                                                                                                                                                                             |                                                       |  |  |  |  |

|                                                          | Гin               | ne: 3          | Note: Answer FIVE full questions, selecting<br>at least TWO questions from each part.                                                                                                                                       | Marks:100                                             |  |  |  |  |

| and mut on                                               | 1                 | a.             | neat diagram.                                                                                                                                                                                                               | lower with a<br>(10 Marks)                            |  |  |  |  |

|                                                          |                   |                | Define:<br>i) Clock based system,<br>ii) Event based system,<br>iii) Interactive based system.<br>Write any four responsibilities of control engineer.                                                                      | (06 Marks)<br>(04 Marks)                              |  |  |  |  |

| - 0 - 74 - 97 IMII M                                     | 2                 | a.<br>b.       | <ul> <li>What do you mean by adaptive control? With a neat diagram, explain any adaptive control.</li> <li>Explain the following: <ol> <li>Supervisory control system,</li> <li>Distributive system.</li> </ol> </li> </ul> | (10 Marks)                                            |  |  |  |  |

|                                                          | 3                 | a.<br>b.       | Explain parallel computers concepts with SISD, SIMD, MIMD and MI advantages and disadvantages.<br>Explain process related interface with suitable example.                                                                  | (10 Marks)<br>SD with its<br>(10 Marks)<br>(10 Marks) |  |  |  |  |

|                                                          | 4                 | a.<br>b.<br>c. | How do strong data typing contribute to the security of programming language?<br>Explain the approaches of application oriented software.<br>What is cutlass and what are the major requirements of CUTLASS?                | (06 Marks)<br>(08 Marks)<br>(06 Marks)                |  |  |  |  |

|                                                          | 5                 | a.<br>b.<br>c. | $\frac{PART - B}{PART - B}$ With a neat block diagram, explain the typical structure of RTOS.<br>What is meant by code sharing? Explain reusable and reentrant code.<br>Define: i) Live lock, ii) Dead lock.                | (10 Marks)<br>(07 Marks)<br>(03 Marks)                |  |  |  |  |

|                                                          | 6                 | a.<br>b.<br>c. | Explain: i) Task chaining and swapping, ii) Task overlaying.<br>Explain the task management system with states of tasks.<br>Explain scheduling policies.                                                                    | (07 Marks)<br>(07 Marks)<br>(06 Marks)                |  |  |  |  |

|                                                          | 7                 | a.<br>b.       | Explain the different phases involved in the design of RTS.<br>Explain foreground and background system with flow chart.                                                                                                    | (10 Marks)<br>(10 Marks)                              |  |  |  |  |

|                                                          | 8                 | a.<br>b.<br>c. | Explain Yourdon methodology.<br>Explain with relevant diagrams the Ward and Mellor method.<br>Write about the environmental model, with context diagram for drying oven.                                                    | (05 Marks)<br>(07 Marks)<br>(08 Marks)                |  |  |  |  |

\* \* \* \* \*

Important Note : 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. 2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice.